Un sencillo tutorial sobre circuitos lógicos en el que se programará un flip flop en VHDL utilizando un FPGA NEXYS 2

En teoría de circuitos lógicos se da a conocer un dispositivo electrónico llamado flip flop, catalogado como un elemento de memoria conformado por compuertas lógicas. Donde éstas a través de una configuración específica, pueden de cierta manera almacenar información. Una de las características principales de un flip flop es su sensibilidad a ciertas entradas prioritarias; es decir, si estas entradas se activan, no importa lo que haya en las demás entradas, se producirá un cambio en la salida dependiendo de lo que se requiera.

En teoría de circuitos lógicos se da a conocer un dispositivo electrónico llamado flip flop, catalogado como un elemento de memoria conformado por compuertas lógicas. Donde éstas a través de una configuración específica, pueden de cierta manera almacenar información. Una de las características principales de un flip flop es su sensibilidad a ciertas entradas prioritarias; es decir, si estas entradas se activan, no importa lo que haya en las demás entradas, se producirá un cambio en la salida dependiendo de lo que se requiera.

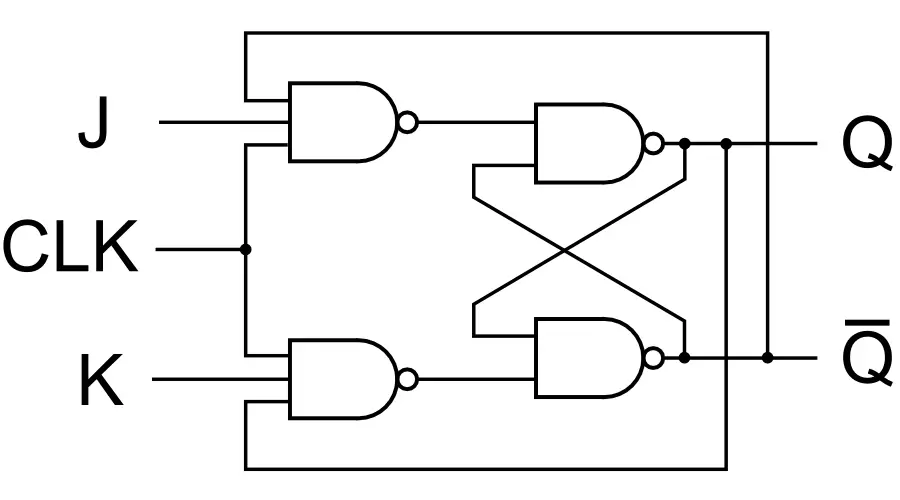

Explicando un poco el funcionamiento de estos dispositivos, podremos programar un flip flop en VHDL, del tipo tipo JK. En la industria, existen muchos flips flops: tipo D, tipo JK, tipo SR, entre otros.

El flip flop JK se dice así en memoria del señor Jack Kilby el creador de los circuitos integrados. En este caso explicaremos el funcionamiento básico:

El dispositivo poseé tres entradas: J, K, reloj. La entrada de reloj es porque en circuitos lógicos, muchos dispositivos se manejan a través de pulso de reloj que le indicarán cuándo debe determinar una acción. Además de esto, se tienen dos salidas clásicas: Q y Q’; estas salidas son complementarias, ya que una es la inversa de la otra. Recuerden que estos dispositivos generalmente trabajan con valores binarios (0 ó 1).

En los sistemas síncronos, los tiempos exactos en los que cualquier entrada cambia de estado se determina en base a la señal de reloj. Las señales de reloj por lo general suelen ser un tren de pulsos rectangulares o una onda cuadrada, que tienen una propiedad llamada transición, esto es cuando se cambia de un valor a otro (0 ó 1). Bien, para los flip flops sincronizados por reloj como el JK, se necesita saber cómo lo vamos a trabajar en base a la transición de la señal de pulso de reloj, es decir si el flip flop cambiará de valor cuando haya una transición de pendiente positiva o negativa.

La transición de pendiente positiva es aquella donde el cambio se da de 0 para 1, mientras que la transición de pendiente negativa es cuando el cambio se da de 1 para 0. En base a esta información se deduce que el flip flop para cambiar lo que hay en su salida necesita de la transición de pulso que envia el reloj ya que esto indica CUÁNDO cambiar de valor la salida, mientras que las entradas de control J y K nos indicará a QUÉ estado cambiará la salida.

Presentamos entonces la tabla de verdad del flip flop JK:

| J | K | CLK | Q |

| 0 | 0 | FPN | Q (sin cambio) |

| 1 | 0 | FPN | 1 |

| 0 | 1 | FPN | 0 |

| 1 | 1 | FPN | Q’ (conmuta) |

FPN = Flancos por Pendiente Negativa. Esto quiere decir que el flip flop a programar trabajará siendo bajo activo.

Como mencionamos, el flip flop responde a ciertas entradas prioritarias en este caso usaremos CLEAR y PRESET. Donde CLEAR es una entrada que pone a la salida del flip flop un 0, mientras que PRESET es una entrada que pone a la salida del flip flop un 1. En flip flop programables y comerciales estas entradas pueden ser bajo o alto activo, nuestro caso como es programable podemos indicar de qué tipo será.

Ahora que hemos terminamo de explicar un poquito sobre el funcionamiento del flip flop JK, expondré el código en VHDL. Este código lo creé hace unos meses cuando trabajé con un FPGA NEXYS 2, estaba trabajando específicamente en un contador binario de 4 bits. Pueden tomar como referencia el código y hacerle modificaciones. Se agradece comentarios =)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

entity FF is Port ( clk,j,k,prn,clrn: in bit; q: out bit); end FF; architecture sintaxis1 of FF is SIGNAL qestado: bit; begin PROCESS (clk,prn,clrn) --Responde a cualquiera de estas entradas BEGIN IF prn = '1' THEN QESTADO <= '1'; ELSIF clrn = '1' THEN QESTADO <= '0'; ELSIF CLK = '0' AND CLK'EVENT THEN --Bajo activo IF J = '1' AND K = '1' THEN QESTADO <= NOT QESTADO; ELSIF J = '1' AND K = '0' THEN QESTADO <= '1'; ELSIF J = '0' AND K = '1' THEN QESTADO <= '0'; ELSIF J = '0' AND K = '0' THEN QESTADO <= QESTADO; END IF; END IF; END PROCESS; Q <= QESTADO; --Guarda el valor de la señal en la salida de los leds end sintaxis1; |